H-Series Systems¶

Three systems are available to subscription users:

System Model H-Series quantum computers

System Model H-Series emulators

Device-specific syntax checkers

Quantum Computers¶

Trapped ion quantum computers are available to users utilizing the System Model H2 and System Model H1 generation of quantum computers, powered by Honeywell. Both System Model H2 and H1 are not locked into a single configuration, but rather allow for all-to-all-connectivity of qubits in four or more parallel gate zones. The System Model H1 architecture consists of a linear trap while the System Model H2 architecture consists of a loop architecture with two linear traps. The base trap architecture for both hardware generations is known as a Quantum Charge-Coupled Device (QCCD)[1].

Individual machines that use the System Model H2 generation of ion traps are designated by the H2-X nomenclature while machines using the System Model H1 generation of ion traps are designated by the H1-X nomenclature. All devices under the H2-X or H1-X nomenclature use the same ion trap design, but at times may have a different number of parallel gate zones, maximum available qubits, and specific performance metrics. At all times, the performance of the quantum computers will have errors not exceeding the maximum errors listed in the Product Data Sheets:

Generational Hardware Nomenclature¶

System Model H*X* refers to a generation of quantum computing hardware using ion traps with a specific geometry. Individual machines tare designated by the HX-Y nomenclature. For example, System Model H1 refers to a generation of quantum computing hardware using ion traps with a single linear geometry. Individual machines that use this generation of ion traps are designated by the H1-X nomenclature, e.g. H1-1. System Model H2 refers to a generation of quantum computing hardware using ion traps with two connected linear sections in a racetrack geometry. Individual machines that use this generation of ion traps are designated by the H2-X nomenclature, e.g. H2-1.

Syntax Checkers¶

The syntax checkers are provided to check program syntax and are specific to each device. Before submitting quantum circuits to the Quantinuum quantum computers or emulator, use of a syntax checker is highly recommended. Jobs submitted to the Quantinuum hardware are in OpenQASM or QIR format. The syntax checker enables checking of the code to ensure it will run before being submitted to the quantum computers or emulator. Access to a syntax checker corresponds to the quantum computers available in a user’s subscription.

If the code compiles, the syntax checker will return a completed status, the cost of the circuit in H-System Quantum Credits (HQCs), and results of all 00. Submission to the syntax checker does not incur a HQC cost and the returned cost will not be accounted for until the circuit is submitted to an emulator or quantum computer backend. If the code does not compile, the syntax checker will return a failed status and give the error returned.

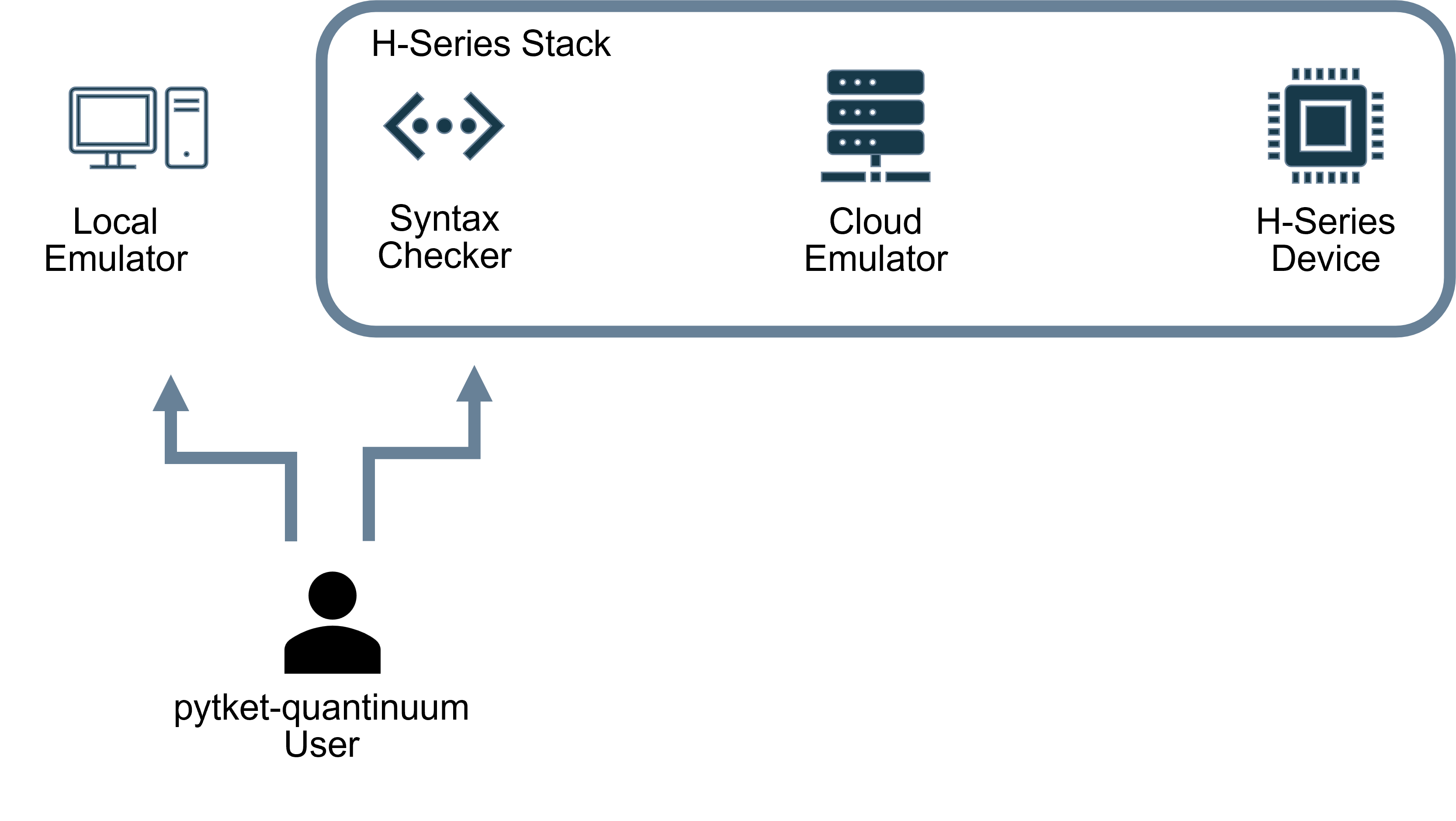

A schematic showing the prerequisite steps before accessing hardware, involving the syntax-checkers and the emulators.¶

API Interface¶

Communication with Quantinuum H-Series endpoints occurs through an API endpoint based on the OpenQASM 2.0 standard [2]. Interface details are given in the Quantinuum Application Programming Interface (API) Specification. This documentation details examples in TKET [3]. The interface to H-Series, pytket-quantinuum, internally translates TKET programs into OpenQASM instructions before submission via the Quantinuum API.